NvSRAM

From HandWiki - Reading time: 4 min

From HandWiki - Reading time: 4 min

nvSRAM is a type of non-volatile random-access memory (NVRAM).[1][2] nvSRAM extends the functionality of basic SRAM by adding non-volatile storage such as EEPROM or flash memory to the SRAM chip. In operation, data is written to and read from the SRAM portion with high-speed access; the data in SRAM can then be stored into or retrieved from the non-volatile storage at lower speeds when needed.

nvSRAM is one of the advanced NVRAM technologies that are fast replacing the battery-backed static random-access memory (BBSRAM), especially for applications that need battery-free solutions and long-term retention at SRAM speeds. nvSRAMs are used in a wide range of situations: networking, aerospace, and medical, among many others[3] where the preservation of data is critical and where batteries are impractical.

Description

When reading and writing data, a nvSRAM acts no differently than a standard asynchronous SRAM. The attached processor or controller sees an 8-bit SRAM interface and nothing else. An added STORE operation stores data that is in an SRAM array in the non-volatile part. Cypress and Simtek nvSRAM have three ways to store data in the non-volatile area. They are:

- autostore: happens automatically when the data main voltage source drops below the device's operating voltage. When this occurs, the power control is switched from VCC to a capacitor. The capacitor will power the chip long enough to store the SRAM contents into the non-volatile part.

- hardware store: the HSB (Hardware Store Busy) pin externally initiates a non-volatile hardware store operation. Using the HSB signal, which requests a non-volatile hardware STORE cycle, is optional.

- software store: is initiated by a certain sequence of operations. When the defined operations are done in sequence the software store is initiated.

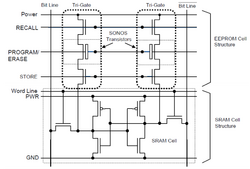

nvSRAM with SONOS technology

SONOS is a cross-sectional structure of MOSFET used in Non-volatile memory such as EEPROM and flash memories. nvSRAM combines the standard SRAM cells with EEPROM cells in SONOS technology[4] to provide a fast read/write access and 20 years of data retention without power. The SRAM cells are paired one-to-one with EEPROM cells. The nvSRAMs are in the CMOS process, with the EEPROM cells having a SONOS stack to provide nonvolatile storage. When normal power is applied, the device looks and behaves in a similar manner as a standard SRAM. However, when power drops out, each cell’s contents can be stored automatically in the nonvolatile element positioned above the SRAM cell. This nonvolatile element uses standard CMOS process technology to obtain the high performance of standard SRAMs. In addition, the SONOS technology is highly reliable and supports 1 million STORE operations

The SONOS memory[5] uses an insulating layer such as silicon nitride with traps as the charge storage layer. The traps in the nitride capture the carriers injected from the channel and retain the charge. This type of memory is also known as “Charge Trap Memory.” Since the charge storage layer is an insulator, this storage mechanism is inherently less sensitive to the tunnel oxide defects and is more robust for data retention. In SONOS, the Oxide-Nitride-Oxide(ONO) stack is engineered to maximize the charge-trapping efficiency during erase and program operations and minimize the charge loss during the retention by controlling the deposition parameters in the ONO formation.

Advantages of SONOS technology:

- lower voltages required for program/erase operations compared to floating-gate MOSFET

- Inherently less sensitive to the tunnel oxide defects

- Robust data retention

Applications

- Data logging

- POS terminals/smart terminals

- Terminals can store payment transaction records locally for later processing, reducing delays and intrusion vulnerability.

- Motor vehicle crash boxes

- Medical equipment

- High-end servers

- Environments where batteries for BBSRAMs are unfeasible

- Remote devices where field service is unfeasible

Comparisons with other types of memories

| nvSRAM | BBSRAM | Ferroelectric RAM | Magnetoresistive random-access memory | |

|---|---|---|---|---|

| Technique | Has non-volatile elements along with high performance SRAM | Has a lithium energy source for power when external power is off | Has a ferroelectric crystal between two electrodes to form a capacitor. The moment of atoms on application of electric field is used to store data | Similar to ferroelectric RAM, but the atoms align themselves in the direction of an external magnetic force. This effect is used to store data |

| Data retention | 20 yrs | 7 yrs, dependent on battery and ambient temperature | 10 yrs | 20 yrs |

| Endurance | Unlimited while powered | Limited to battery life | 1010 to 1014 [6][7] | 108 [8] |

| Store mechanism | Autostore initiated when VCC power down is detected. | Chip enable must be maintained at high logic to prevent inadvertent read/writes. | Static operation. Data is stored in the non-volatile part only. | |

| Power up data restore | Non-volatile data is made available automatically in the SRAM. | SRAM will switch from battery to VCC. | ||

| Substitution with SRAM | nvSRAM can be substituted for SRAM with minor board modification to add external capacitor. | Provision for battery necessitates board redesign to accommodate a bigger size for the battery | Some parts are pin-to-pin compatible with existing SRAMs. | Pin-to-pin compatible with existing SRAMs |

| Soldering | Standard SMT used | Reflow solder cannot be done with battery installed as batteries may explode. | Standard SMT used | |

| Speed (best) | 15–45 ns | 70–100 ns | 55 ns | 35 ns |

References

- ↑ Ma, Yanjun; Kan, Edwin (2017) (in en). Non-logic Devices in Logic Processes. Springer. ISBN 9783319483399. https://books.google.com/books?id=1_iODgAAQBAJ&q=nvSRAM&pg=PA211.

- ↑ Xie, Yuan (2013) (in en). Emerging Memory Technologies: Design, Architecture, and Applications. Springer Science & Business Media. ISBN 9781441995513. https://books.google.com/books?id=k8-4BAAAQBAJ&q=nvSRAM&pg=PA103.

- ↑ Computer organization. (4th ed.). [S.l.]: McGraw-Hill. 1996. ISBN 0-07-114323-8. https://archive.org/details/isbn_9780071143097.

- ↑ "Nonvolatile SRAM (nvSRAM) Basics". https://www.cypress.com/file/46216/download.

- ↑ Ramkumar, Krishnaswamy; Prabhakar, Venkataraman; Geha, Sam. "Cypress SONOS Technology". https://www.cypress.com/file/123341/download.

- ↑ "Memory FRAM – 4 M Bit (512 K × 8) – MB85R4001A". https://www.fujitsu.com/us/Images/MB85R4001A-DS501-00005-3v0-E.pdf.

- ↑ "4-Mbit (256 K × 16) F-RAM Memory". http://www.cypress.com/file/136476/download.

- ↑ "StackPath". 21 March 2018. http://www.electronicdesign.com/industrial-automation/unleashing-mram-persistent-memory.

External links

- nvSRAM product site | Cypress Semiconductor

- APP2372: A Comparison between Battery Backed NV SRAMs and NOVRAMS | Maxim Integrated

- MRAM Replaces nvSRAM | Everspin Technologies Inc.

|

KSF

KSF